# LCD Module User Manual EDM 640240-01

| REVISION RECORD              |                       |  |  |  |

|------------------------------|-----------------------|--|--|--|

| REV. NO. DATA REVISION ITEMS |                       |  |  |  |

| 1.0                          | First Release Version |  |  |  |

# **Contents**

| 1.Scope4                |

|-------------------------|

| 2.Warranty4             |

| 3.Features4             |

| 4.MechanicalDiagram7    |

| 5.I/OTerminal7          |

| 6.QualityLevel14        |

| 7.Reliability17         |

| 8.HandlingPrecautions17 |

| 9.PrecautionforUse18    |

# 1.Scope

This manual defines general provisions as well as inspection standards for standard LCD module. If the event of unforeseen problem or unspecified items may occur, please contact the nearest supplier or our company.

# 2.Warranty

If module is not stored or used as specified in this manual, it will be void the 12- month warranty.

# 3.Features

## 3-1. Features

(1) Display mode: Transflactive/positive

FSTN LCD

(2) Display color: Display dots: Black

Background: White

(3) Display Format: 640(w)×240(h) full dots

(4) Input data: 8-bit parallel data interfaced from a MPU

(5) Multiplex ratio: 1/240 Duty, 1/16Bias

(6) Viewing direction: 6 O'clock(7) Back light: LED White(8) Controller: SID13700

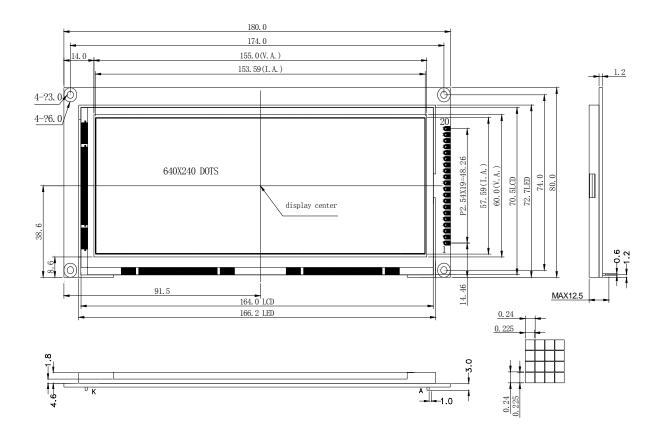

#### 3-2. Mechanical features

| Item               | Specifications                | Unit |

|--------------------|-------------------------------|------|

| Outline dimensions | 180.0(W)×80.0(H) ×12.5Max.(T) | mm   |

| Viewing Area       | 155.0(W)×60.0(H)              | mm   |

| Image Area         | 153.59(W)×57.59(H)            | mm   |

| Number of Dots     | 640 (W)×240(H)                |      |

| Dot Size           | 0.225(W)×0.225(H)             | mm   |

| Dot Pitch          | 0.24(W)×0.24(H)               | mm   |

#### 3-3. Absolute maximum ratings

| Item                   | Symbol | Condition   | Min  | Max      | Units                                                                              |

|------------------------|--------|-------------|------|----------|------------------------------------------------------------------------------------|

| Deven somehofenlerie   | HVdd   | <b>2</b> 5℃ | -0.3 | 7.0      |                                                                                    |

| Power supply for logic | LVdd   | <b>2</b> 5℃ | -0.3 | 4.0      | V                                                                                  |

| looset valta aa        | HVin   | <b>2</b> 5℃ | -0.3 | HVdd+0.5 |                                                                                    |

| Input voltage          | LVin   | <b>2</b> 5℃ | -0.3 | LVdd+0.5 | V                                                                                  |

|                        | HVout  | <b>2</b> 5℃ | -0.3 | HVdd+0.5 | .,                                                                                 |

| Output voltage         | LVout  | <b>2</b> 5℃ | -0.3 | LVdd+0.5 | V                                                                                  |

| Operating temperature  | Тор    |             | -40  | 80       | $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

| Storage temperature    | Tstg   |             | - 65 | 150      | $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

NOTE:

- (1) When using a power supply with high impedance,a large potential difference between the chip's internal power supply voltage and the input voltage may occur, thus making the power supply susceptible to latch-up. Therefore, pay particular attention to the power supply and its wiring.

- (2) All voltage are based on Vss=0.

- (3) The symbol H\*\*\*indicates 5V-block pins;L\*\*\* indicates 3.3V-block pins

# **3-4Electrical Characteristics**

$[V_{SS} = 0V, HV_{DD} = 4.5 - 5.5V, Ta = -40 - 85^{\circ}C]$

| Doministra                                                                  | Symbol            | Test Condition                                        |                       | Rated Value | 4.5 – 5.5 v, 1a | Unit |

|-----------------------------------------------------------------------------|-------------------|-------------------------------------------------------|-----------------------|-------------|-----------------|------|

|                                                                             |                   | Mir                                                   |                       | Тур.        | Max.            | Unit |

| Input Leakage Current                                                       | $I_{LI}$          | _                                                     | -1                    | _           | 1               | uА   |

| OFF-state Leakage Current                                                   | $I_{OZ}$          | —Note 2)                                              | -1                    | _           | 1               | uА   |

| High Level Output Voltage                                                   | VoH               | $I_{OH} = -8.0 \text{mA}$<br>$HV_{DD} = Min$          | HV <sub>DD</sub> -0.4 | _           | _               | v    |

| Low Level Output Voltage                                                    | Vol               | I <sub>OL</sub> = 8.0m<br>HV <sub>DD</sub> =Min       | _                     | _           | 0.4             | v    |

| High Level Input Voltage                                                    | V <sub>IH1</sub>  | CMOS level<br>HV <sub>DD</sub> = Max                  | 3.5                   | _           | _               | v    |

| Low Level Input Voltage                                                     | VIL1              | CMOS level<br>HV <sub>DD</sub> = Min                  | _                     | _           | 1.0             | v    |

| Positive Trigger Voltage                                                    | $V_{T1+}$         | CMOS Schmitt                                          | 2.0                   | _           | 4.0             | V    |

| Negative Trigger Voltage                                                    | V <sub>T1</sub> . | CMOS Schmitt                                          | 0.8                   | _           | 3.1             | V    |

| Hysteresis Voltage                                                          | VH1               | CMOS Schmitt                                          | 0.3                   | _           | _               | V    |

| High Level Input Voltage                                                    | $V_{\rm IH2}$     | TTL level<br>HV <sub>DD</sub> = Max                   | 2.0                   | _           | _               | v    |

| Low Level Input Voltage                                                     | $V_{IL2}$         | TTL level<br>HV <sub>DD</sub> = Min                   | _                     | _           | 0.8             | v    |

| Pulldown Resistance                                                         | R <sub>PD</sub>   | $VI = HV_{DD}$                                        | 30                    | 60          | 144             | kΩ   |

| Operating Supply Current                                                    | I <sub>opr</sub>  | f <sub>OSC</sub> =10 MHz<br>Nonloaded<br>256 x 200dot | _                     | TBD         | TBD             | mA   |

| Quiescent Supply Current<br>(between HV <sub>DD</sub> and V <sub>SS</sub> ) | IQн               | Sleep mode<br>XCG1, CS#, RD# = V <sub>DD</sub>        |                       | _           | 30              | uA   |

| Quiescent Supply Current<br>(between LVDD and Vss)                          | I <sub>QH</sub>   | Sleep mode<br>XCG1, CS#, RD# = V <sub>DD</sub>        | _                     | _           | 35              | uA   |

- Note: 1. The pulse applied to the RESET# pin must be held low for 200 μs or more to be effective. However, avoid keeping the input pulse active for more than several seconds because the LCD's d.c. drive capability may be adversely affected.

- The VB0-DB7 pins come with a feedback circuit, so that even when input becomes high impedance, the pins retain the state held immediately before. Therefore, input voltage of an intermediate level allows input current to flow to the pin.

$[V_{SS} = 0V, VDD = LV_{DD} = 3.3 - 0.3V, Ta = -40 - 85^{\circ}C]$

| Barrandan                                                                   | 0                 | Took Oou dilico                                                        |                       | Rated Value |      | Unit  |  |

|-----------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------|-----------------------|-------------|------|-------|--|

| Parameter                                                                   | Symbol            | Test Condition                                                         | Min.                  | Тур.        | Max. | Offic |  |

| Input Leakage Current                                                       | $I_{LI}$          | _                                                                      | -1                    | _           | 1    | uА    |  |

| OFF-state Leakage Current                                                   | Ioz               | — Note 2)                                                              | -1                    | _           | 1    | uA    |  |

| High Level Output Voltage                                                   | Von               | $\begin{split} &I_{OH} = -6.0 \text{mA} \\ &HV_{DD} = Min \end{split}$ | HV <sub>DD</sub> -0.4 | -           | -    | v     |  |

| Low Level Output Voltage                                                    | V <sub>OL</sub>   | I <sub>OL</sub> = 6.0m<br>HV <sub>DD</sub> =Min                        | _                     | -           | 0.4  | v     |  |

| High Level Input Voltage                                                    | V <sub>IH1</sub>  | LVTTL level<br>V <sub>DD</sub> = Max                                   | 2.0                   | _           | -    | v     |  |

| Low Level Input Voltage                                                     | V <sub>IL1</sub>  | LVTTL level<br>V <sub>DD</sub> = Min                                   | _                     | _           | 0.8  | v     |  |

| Positive Trigger Voltage                                                    | V <sub>T1</sub> + | LVTTL Schmitt                                                          | 1.1                   | _           | 2.4  | V     |  |

| Negative Trigger Voltage                                                    | V <sub>T1</sub> . | LVTTL Schmitt                                                          | 0.6                   | _           | 1.8  | V     |  |

| Hysteresis Voltage                                                          | $V_{H1}$          | LVTTL Schmitt                                                          | 0.1                   | _           | _    | V     |  |

| Pulldown Resistance                                                         | RpD               | $VI = V_{DD}$                                                          | 20                    | 50          | 120  | kΩ    |  |

| Operating Supply Current                                                    | Iopr              | f <sub>OSC</sub> =10 MHz<br>Nonloaded<br>256 x 200dot                  | _                     | TBD         | TBD  | mA    |  |

| Quiescent Supply Current<br>(between LV <sub>DD</sub> and V <sub>SS</sub> ) | $I_{\mathrm{QH}}$ | Sleep mode<br>XCG1, CS#, RD# = V <sub>DD</sub>                         | _                     | _           | 35   | uА    |  |

# **3-5 Electro-optical Characteristics**

| Ite                                       | em                     | Symbol | Conditions  | Min. | Тур. | Max. | Unit |

|-------------------------------------------|------------------------|--------|-------------|------|------|------|------|

| LCD Driving Voltage (Recommended voltage) |                        | Von I  |             | -    |      |      |      |

|                                           |                        |        |             | -    | 18.4 |      | V    |

| (Recommen                                 | ided vollage)          |        | <b>70</b> ℃ |      |      |      |      |

| Current                                   | lania                  | الماما |             | 1    | 500  | 700  |      |

| consumpti                                 | logic                  | ldd    | Vdd=5V      | 1    | 200  | 250  |      |

| on(No                                     | I CD drive             | loo    | Fflm=75Hz   |      | 540  | 810  | uA   |

| B/L)                                      | LCD drive              | lee    |             | 1    | 250  | 300  |      |

| Power sup                                 | Power supply for logic |        | <b>25</b> ℃ | 2.7  | _    | 5.5  | ٧    |

# 3-6 LED back light specifications

| Item            |              | Standard Values |           |      |           |

|-----------------|--------------|-----------------|-----------|------|-----------|

| item            | Unit         | Min.            | Тур.      | Max. | Condition |

| Supply Voltage  | V            | 1               | 3.2       |      |           |

| Current         | mA           |                 | 150       |      |           |

| Luminous Color  |              |                 | W hite    |      |           |

| Operating Temp. | $^{\circ}$ C | -20 ~ +70       |           | _    |           |

| Storage Temp.   | $^{\circ}$ C |                 | -30 ~ +80 |      | _         |

# 4. Mechanical Diagram

# 5.I/O Terminal

## 5-1 I/O Connection

| Pin No. | Symbol  | Function                            |

|---------|---------|-------------------------------------|

| 1       | Vss     | GND                                 |

| 2       | Vdd     | POWER SUPPLY FOR LOGIC              |

| 3       | V0      | DRIVING VOLTAGE FOR LCD             |

| 4       | A0      | DATA TYPE SELECT                    |

| 5       | /WR     | 8080:WRITE SIGNAL 6800:R/W SIGNAL   |

| 6       | /RD     | 8080:READ SIGNAL 6800:ENABLE SIGNAL |

| 7-14    | DB0-DB7 | DATA BUS LINE                       |

| 15      | /CS     | CHIP SELECT,ACTIVEL                 |

| 16      | /RES    | CONTROLLER RESET SIGNAL             |

| 17      | VEE     | NEGATIVE VOLTAGE OUTPUT             |

| 18      | CNF3    | H:6800 L:8080                       |

| 19      | LED+    | BACKLIGHT VOLTAGE+                  |

| 20      | LED-    | BACKLIGHT VOLTAGE-                  |

# 5-2 Signal timing diagram

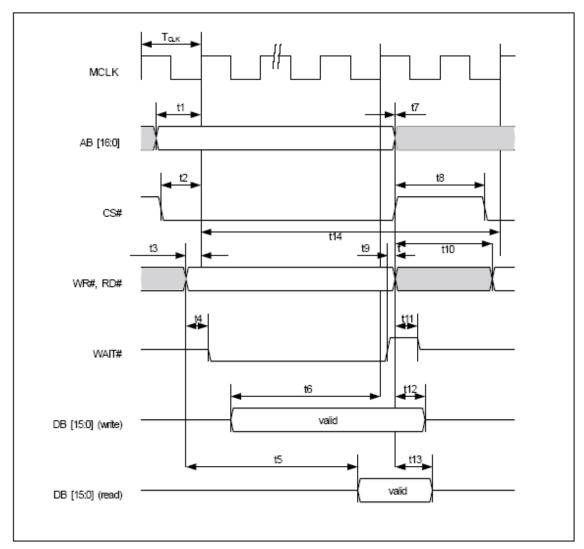

# 5-2-1 8080 family interface Timing

<sup>\*</sup> MCLK denotes CLKI or the internally generated system clock.

# LCD Module User Manual

# Gemeric Bus Interface Timing

$[V_{SS} = 0V, V_{DD} = 4.5 - 5.5V, Ta = -40 - 85^{\circ}C]$

| 0         | B                                                                                                                            | S                               | pec  | 1.174            |

|-----------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------------------|

| Symbol    | Parameter -                                                                                                                  | Min.                            | Max. | Unit             |

| $f_{CLK}$ | BUS clock frequency                                                                                                          | _                               | 64   | MHz              |

| TCLK      | BUS clock period                                                                                                             | 1/fclk                          | _    | ns               |

| tl        | AB [16 : 0] setrup to first CLK rising edge where CS# = 0 and either RD# = 0 or WR# = 0                                      | 11                              | _    | ns               |

| t2        | CS# setup to CLK rising edge                                                                                                 | 9                               | _    | ns               |

| t3        | RD#, WR# setup to CLK rising edge                                                                                            | 9                               | _    | ns               |

| t4        | RD#, WR# state change to WAIT# driven low                                                                                    | 1                               | 5    | ns               |

| ť         | RD# falling edge to DB [15:0] driven (ead cycle)                                                                             | 3Te+9ns                         | _    | Telk             |

| t6        | DB [15:0] setup to 4th rising CLK edge after CS# = 0 and WR# = 0                                                             | 1                               | _    | T <sub>CLK</sub> |

| t7        | AB [16:0], CS# hold from RD#, WR# rising edge                                                                                | 8                               | _    | ns               |

| t8        | CS# deasserted to reasserted  - When read  - when Write (next cycle = write cycle)  - when Write (next cycle = read cycle)   | lTelk<br>2Telk+8ns<br>5Telk+8ns | _    | ns<br>ns<br>ns   |

| t9        | WAIT# rising edge to RD#, WR# rising edge                                                                                    | 0                               | _    | ns               |

| t10       | WR#, RD# deasserted to reasserted - When read - when Write (next cycle = write cycle) - when Write (next cycle = read cycle) | 1Telk<br>2Telk+8ns<br>5Telk+8ns | _    | ns<br>ns<br>ns   |

| tll       | Rising edge of either RD# or WR# to WAIT# high impedance 0.5 TCLK                                                            | _                               | 0.5  | T <sub>CLK</sub> |

| t12       | D [15:0] hold from WR# rising edge (write cycle)                                                                             | 1                               | _    | ns               |

| t13       | D [15:0] hold from RD# rising edge (read cycle)                                                                              | 1                               | _    | ns               |

| t14       | Cycle Length Read Write (next write cycle) Write (next read cycle)                                                           | 6<br>7<br>10                    | _    | T <sub>CLK</sub> |

## Gemeric Bus Interface Timing

[V<sub>SS</sub> = 0V, V<sub>DD</sub> = 3.0 - 3.6V, Ta = -40 - 85°C]

| Complete  | Description                                                                                                                  | S <sub>1</sub>                    | pec  | Unit             |

|-----------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|------------------|

| Symbol    | Parameter                                                                                                                    | Min.                              | Max. | Unit             |

| $f_{CLK}$ | BUS clock frequency                                                                                                          | _                                 | 64   | MHz              |

| TCLK      | BUS clock period                                                                                                             | $1/f_{\rm CLK}$                   | _    | ns               |

| tl        | AB [16 : 0] setrup to first CLK rising edge where CS# = 0 and either RD# = 0 or WR# = 0                                      | 12                                | _    | ns               |

| t2        | CS# setup to CLK rising edge                                                                                                 | 11                                | _    | ns               |

| t3        | RD#, WR# setup to CLK rising edge                                                                                            | 11                                | _    | ns               |

| t4        | RD#, WR# state change to WAIT# driven low                                                                                    | 1                                 | 7    | ns               |

| t5        | RD# falling edge to DB [15:0] driven (ead cycle)                                                                             | 3Te+llns                          | _    | Telk             |

| t6        | DB [15:0] setup to 4th rising CLK edge after CS# = 0 and WR# = 0                                                             | 1                                 | _    | T <sub>CLK</sub> |

| t7        | AB [16:0], CS# hold from RD#, WR# rising edge                                                                                | 10                                | _    | ns               |

| t8        | CS# deasserted to reasserted  - When read  - when Write (next cycle = write cycle)  - when Write (next cycle = read cycle)   | 1Telk<br>2Telk+10ns<br>5Telk+10ns | _    | ns<br>ns<br>ns   |

| t9        | WAIT# rising edge to RD#, WR# rising edge                                                                                    | 0                                 | _    | ns               |

| t10       | WR#, RD# deasserted to reasserted - When read - when Write (next cycle = write cycle) - when Write (next cycle = read cycle) | 1Telk<br>2Telk+10ns<br>5Telk+10ns | _    | ns<br>ns<br>ns   |

| tll       | Rising edge of either RD# or WR# to WAIT# high impedance 0.5 TCLK                                                            | _                                 | 0.5  | T <sub>CLK</sub> |

| t12       | D [15:0] hold from WR# rising edge (write cycle)                                                                             | 1                                 | _    | ns               |

| t13       | D [15:0] hold from RD# rising edge (read cycle)                                                                              | 1                                 | _    | ns               |

| tl4       | Cycle Length Read Write (next write cycle) Write (next read cycle)                                                           | 6<br>7<br>10                      | _    | T <sub>CLK</sub> |

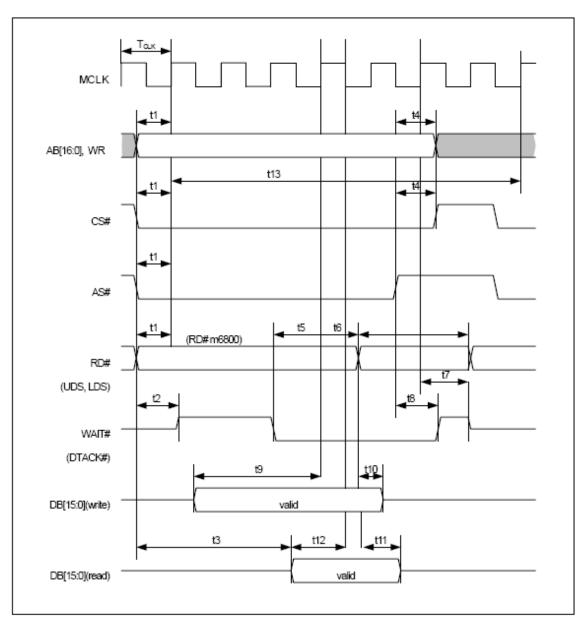

# 5-2-2 System Bus Read/write characteristics II (MC68K-series MPU)

<sup>\*</sup> MCLK denotes CLKI or the internally generated system clock.

# LCD Module User Manual

#### Motorola M68K#1 Interface Timing

$[V_{SS} = 0V, V_{DD} = 4.5 - 5.5V, Ta = -40 - 85^{\circ}C]$

| -         | <b>.</b>                                                                                                                                      |                                 |                      | <del></del>      |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------|------------------|

| Symbol    | Parameter                                                                                                                                     | S                               | Unit                 |                  |

| Symbol    | raiallicici                                                                                                                                   | Min.                            | Max.                 | Onit             |

| $f_{CLK}$ | BUS clock frequency                                                                                                                           | _                               | 64                   | MHz              |

| TCLK      | BUS clock period                                                                                                                              | 1/f <sub>CLK</sub>              | _                    | ns               |

| tl        | AB [16 : 0], WR# (R/W#) and CS# and AS# and RD# (UDS#, LDS#) setup to first CLK rising edge $$                                                | 9                               | _                    | ns               |

| t2        | CS# and AS# asserted to WAIT# (DTACK#) driven                                                                                                 | 1                               | 7                    | ns               |

| t3        | RD# = 0 (UDS# = 0 or LDS# = 0) to DB [15:0] driven (read cycle)                                                                               | 3Telk+9ns                       | _                    | ns               |

| t4        | AB [16:0], WR# (R/W#) and CS# hold from AS# rising edge                                                                                       | 0                               | _                    | ns               |

| t5        | WAIT# (DTACK#) falling edge to RD# (UDS#, LDS#) rising edge                                                                                   | 1                               | _                    | T <sub>CLK</sub> |

| t6        | RD# (USD#, LDS#) deasserted high to reasserted low - When read - when Write (next cycle = write cycle) - when Write (next cycle = read cycle) | 1Telk<br>2Telk+8ns<br>5Telk+8ns | _                    | ns<br>ns<br>ns   |

| t7        | CLK rising edge to WAIT# (DTACK#) high impedance                                                                                              | _                               | lT <sub>CLK</sub> -2 | ns               |

| t8        | AS# rising edge to WAIT# (DTACK#) rising edge                                                                                                 | 3                               | 12                   | ns               |

| t9        | DB [15:0] valid to 4th CLK rising edge where CS# = 0, AS# = 0 and either RD# = 0 (UDS# = 0 or LDS# = 0) (wirte cycle)                         | 1                               | _                    | TCLK             |

| t10       | DB [15:0] hold from RD# (UDS#, LDS#) falling edge (wirte cycle)                                                                               | 4                               | _                    | ns               |

| tll       | RD# (UDS#, LDS#) rising edge to DB [15:0] high impedance (read cycle)                                                                         | 6                               | _                    | ns               |

| t12       | DB [15 : 0] valid setup time to 2nd CLK falling edge after WAIT#<br>(DTACK#) goes low (read cycle)                                            | 6                               | _                    | ns               |

| t13       | tl3 Cycle Length Read<br>Write (next write cycle)<br>Write (next read cycle)                                                                  | 7<br>8<br>11                    | _                    | T <sub>CLK</sub> |

## Motorola M68K#1 Interface Timing

$[V_{SS} = 0V, V_{DD} = 3.0 - 3.6V, T_a = -40 - 85^{\circ}C]$

|                  |                                                                                                                                               | L * SS - • *, * DD              | - 5.0 - 5.6 v, 1a -  | -40 - 05 - 0     |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------|------------------|--|

| Symbol           | Parameter                                                                                                                                     | S                               | pec                  | Unit             |  |

| Symbol           | Parameter                                                                                                                                     | Min.                            | Max.                 | - Onn.           |  |

| f <sub>CLK</sub> | BUS clock frequency                                                                                                                           | _                               | 64                   | MHz              |  |

| TCLK             | BUS clock period                                                                                                                              | 1/fclk                          | _                    | ns               |  |

| tl               | AB [16 : 0], WR# (R/W#) and CS# and AS# and RD# (UDS#, LDS#) setup to first CLK rising edge $$                                                | 9                               | _                    | ns               |  |

| t2               | CS# and AS# asserted to WAIT# (DTACK#) driven                                                                                                 | 1                               | 10                   | ns               |  |

| t3               | RD# = 0 (UDS# = 0 or LDS# = 0) to DB [15:0] driven (read cycle)                                                                               | 3Tclk+9ns                       | _                    | ns               |  |

| t4               | AB [16:0], WR# (R/W#) and CS# hold from AS# rising edge                                                                                       | 0                               | _                    | ns               |  |

| t5               | WAIT# (DTACK#) falling edge to RD# (UDS#, LDS#) rising edge                                                                                   | 1                               | _                    | T <sub>CLK</sub> |  |

| t6               | RD# (UDS#, LDS#) deasserted high to reasserted low - When read - when Write (next cycle = write cycle) - when Write (next cycle = read cycle) | 1Telk<br>2Telk+8ns<br>5Telk+8ns | _                    | ns<br>ns<br>ns   |  |

| t7               | CLK rising edge to WAIT# (DTACK#) high impedance                                                                                              | _                               | lT <sub>CLK</sub> -2 | ns               |  |

| t8               | AS# rising edge to WAIT# (DTACK#) rising edge                                                                                                 | 3                               | 15                   | ns               |  |

| t9               | DB [15:0] valid to 4th CLK rising edge where CS# = 0, AS# = 0 and either RD# = 0 (UDS# = 0 or LDS# = 0) (wirte cycle)                         | 1                               | _                    | TCLK             |  |

| t10              | DB [15:0] hold from RD# (UDS#, LDS#) falling edge (wirte cycle)                                                                               | 4                               | _                    | ns               |  |

| tll              | RD# (UDS#, LDS#) rising edge to DB [15:0] high impedance (read cycle)                                                                         | 8                               | _                    | ns               |  |

| t12              | DB [15:0] valid setup time to 2nd CLK falling edge after WAIT# (DTACK#) goes low (read cycle)                                                 | 8                               | _                    | ns               |  |

| t13              | Cycle Length Read Write (next write cycle) Write (next read cycle)                                                                            | 7<br>8<br>11                    | _                    | T <sub>CLK</sub> |  |

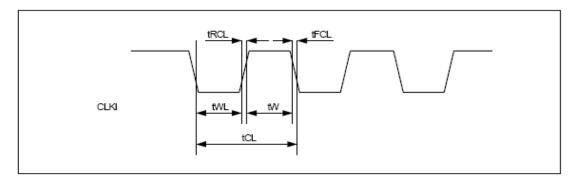

# 5-2-3 External Clock Input Characteristics

$[V_{SS} = 0V, V_{DD} = 4.5 - 5.5V, Ta = -40 - 85^{\circ}C]$

| Symbol           | Parameter                                      |      |      | Unit  |

|------------------|------------------------------------------------|------|------|-------|

| Symbol           | raidificio                                     | Min. | Max. | OIIIL |

| t <sub>RCL</sub> | External input clock rise time                 | _    | 2    | ns    |

| tFCL             | External input clock fall time                 | _    | 2    | ns    |

| twn              | High-level pulse width of external input clock | 7    | _    | ns    |

| t <sub>WL</sub>  | Low-level pulse width of external input clock  | 7    | _    | ns    |

| tcL              | External input clock period                    | 16.4 | _    | ns    |

#### **5-3 MPU INTERFACE**

The S1D13700 uses a combination of CNF2/3/4, AB15-0, RD#, WR#, and CS# to discriminate information supplied to it via the system data bus as described in Section 2.2 "Pin Functions" on page 9.

In indirect interface mode, AB0 generally is connected to the least significant bit of the system address bus. CNF2 and CNF3 are provided for changing the functions of S1D13700 pins 58 and 59 to enable the chip to be connected directly to the 80 or 68-series MPU bus, and are pulled high or low through a resistor when in use. For the 80-series MPU, the S1D13700 should normally be mapped in I/O space.

## 5-3-1 80-series MPU

<Direct access for the 80-series interface>

| С | NF4 | AB15<br>– AB1 | AB0  | RD# | WR# | Function                              |  |  |  |  |

|---|-----|---------------|------|-----|-----|---------------------------------------|--|--|--|--|

|   | 0   | 0orl          | 0orl | 0   | 1   | Read from command/parameter registers |  |  |  |  |

|   | 0   | 0orl          | 0orl | 1   | 1   | Write to command/parameter registers  |  |  |  |  |

<Indirect access for the 80-series interface>

| CNF4 | AB15<br>– AB1 | AB0 | RD# | WR# | Function                                    |

|------|---------------|-----|-----|-----|---------------------------------------------|

| 1    | _             | 0   | 0   | 1   | 1                                           |

| 1    | _             | 1   | 0   | 1   | Data (display data and cursor address) read |

| 1    | _             | 0   | 1   | 0   | Data (display data and parameter) write     |

| 1    | _             | 1   | 1   | 0   | Command write (code only)                   |

5-3-2 68-series MPU

<Direct access for the 68-series interface>

| CNF4 | AB15<br>– AB1 | AB0  | WR#<br>(R/W#) | RD#<br>(E) | Function                              |

|------|---------------|------|---------------|------------|---------------------------------------|

| 0    | 0orl          | 0orl | 1             | 1          | Read from command/parameter registers |

| 0    | 0orl          | 0orl | 0             | 1          | Write to command/parameter registers  |

<sup>&</sup>lt;Indirect access for the 68-series interface>

| CNF4 | AB15<br>– AB1 | AB0 | WR#<br>(R/W#) | RD#<br>(E) | Function                                    |

|------|---------------|-----|---------------|------------|---------------------------------------------|

| 1    |               | 0   | 1             | 1          | _                                           |

| 1    | _             | 1   | 1             | 1          | Data (display data and cursor address) read |

| 1    | _             | 0   | 0             | 1          | Data (display data and parameter) write     |

| 1    | _             | 1   | 0             | 1          | Command write (code only)                   |

# 5-4 display command

When indirect mode is selected for the system interface, use commands to set up the display.

The table below lists the types of commands, including the code of each command.

| Purpose              | Command    | DD DDI DD |     |      |   |   |   |   |   | Command<br>description | Parameters<br>following the<br>command |   | Remarks    |                                                                                    |                      |                                |        |

|----------------------|------------|-----------|-----|------|---|---|---|---|---|------------------------|----------------------------------------|---|------------|------------------------------------------------------------------------------------|----------------------|--------------------------------|--------|

|                      |            | WR#       | RDŧ | ≠AB0 | 7 | 6 |   |   |   |                        | 1                                      | 0 | DB<br>HEX  |                                                                                    | No. of<br>parameters | No. of See<br>parameters pages |        |

| Operation<br>control | SYSTM SET  | 1         | 0   | 1    | 0 | 1 | 0 | 0 | 0 | 0                      | 0                                      | 0 | 40         | Sets initial operation<br>and window size.                                         | 8                    | 19                             |        |

| control              | SLEEP IN   | 1         | 0   | 1    | 0 | 1 | 0 | 1 | 0 | 0                      | 1                                      | 1 | 53         | Sleep operation.                                                                   | 0                    | 27                             | Note 1 |

|                      | DISPON/OFF | 1         | 0   | 1    | 0 | 1 | 0 | 1 | 1 | 0                      | 0                                      | D | 58 •<br>59 | Instructs to turn<br>display on or off and<br>make the screen flash<br>on and off. | 1                    | 28                             | Note 1 |

|                      | SCROLL     | 1         | 0   | 1    | 0 | 1 | 0 | 0 | 0 | 1                      | 0                                      | 0 | 44         | Sets the display start<br>address and display<br>area.                             | 10                   | 29                             |        |

| <b>5</b> . ,         | CSRFORM    | 1         | 0   | 1    | 0 | 1 | 0 | 1 | 1 | 1                      | 0                                      | 1 | 5D         | Sets the cursor shape,<br>etc.                                                     | 2                    | 37                             |        |

| Display<br>control   | CSRDIR     | 1         | 0   | 1    | 0 | 1 | 0 | 0 | 1 | 1                      | CD<br>1                                | 0 | 4C –<br>4F | Sets the direction of<br>cursor movement.                                          | 0                    | 38                             |        |

|                      | OVLAY      | 1         | 0   | 1    | 0 | 1 | 0 | 1 | 1 | 0                      | 1                                      | 1 | 5 <b>B</b> | Instructs screen overlay mode.                                                     | 1                    | 39                             |        |

|                      | CGRAM ADR  | 1         | 0   | 1    | 0 | 1 | 0 | 1 | 1 | 1                      | 0                                      | 0 | 5C         | Sets the start address<br>of CG RAM.                                               | 2                    | 43                             |        |

|                      | HDOT SCR   | 1         | 0   | 1    | 0 | 1 | 0 | 1 | 1 | 0                      | 1                                      | 0 | 5A         | Sets the horizontal<br>direction dot unit and<br>scroll position.                  | 1                    | 44                             |        |

|                      | GRAY SCALE | 1         | 0   | 1    | 0 | 1 | 1 | 0 | 0 | 0                      | 0                                      | 0 | 60         | Sets grayscale mode.                                                               | 0                    | 45                             |        |

| Drawing              | CSRW       | 1         | 0   | 1    | 0 | 1 | 0 | 0 | 0 | 1                      | 1                                      | 0 | 46         | Sets the cursor address.                                                           | 2                    | 45                             | Note 1 |

| control              | CSRR       | 1         | 0   | 1    | 0 | 1 | 0 | 0 | 0 | 1                      | 1                                      | 1 | 47         | Instructs to read the<br>cursor address.                                           | 2                    | 46                             | Note 1 |

| Memory               | MWRITE     | 1         | 0   | 1    | 0 | 1 | 0 | 0 | 0 | 0                      | 1                                      | 0 | 42         | Instructs to write to display memory.                                              | _                    | 47                             | Note 1 |

| control              | MREAD      | 1         | 0   | 1    | 0 | 1 | 0 | 0 | 0 | 0                      | 1                                      | 1 | 43         | Instructs to read display memory data.                                             | _                    | 47                             |        |

Note 1: As a rule, each command is executed every time a parameter for the command is input to the S1D13700, and completed before the next parameter (P) or command (C) is input. Therefore, the MPU can stop sending parameters in the middle and send the next command.

# 6. Quality Level

## **6-1 Inspection conditions**

6-1-1The environmental conditions for inspection shall be as follows:

Room temperature:  $20\pm3^{\circ}$

Humidity:  $65\pm20\%$  RH

6-1-2 The external visual inspection:

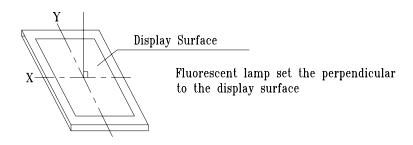

The inspection shall be performed by using a 20W fluorescent lamp for illumination and the distance between LCD and the eyes of the inspector should be at least 30cm.

(1) Light method

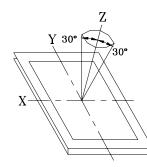

#### (2) Inspection distance and angle

Inspection should be performed within  $\emptyset$  ( $\emptyset$ =30°) from Z axis to each X and Y axis.

Inspection distance of any direction within  $\emptyset$  must be kept 30±50cm to the display surface.

# 6-2 Sampling procedures for each item's acceptance level table

| Defect type  | Sampling procedure              | AQL        |  |  |  |

|--------------|---------------------------------|------------|--|--|--|

|              | MIL-STD-105D Inspection Level I |            |  |  |  |

| Major defect | Normal inspection               | Q/DF-01-06 |  |  |  |

|              | Single sample inspection        |            |  |  |  |

|              | MIL-STD-105D Inspection Level I |            |  |  |  |

| Minor defect | Normal inspection               | Q/DF-01-06 |  |  |  |

|              | Single sample inspection        |            |  |  |  |

#### 6-3 Classification of defects

## 6-3-1 Major defect

A major defect refers to a defect that may substantially degrade usability for product applications.

#### 6-3-2 Minor defect

A minor defect refers to a defect that deviates from existing standards almost unrelated to the effective use of the product or its operation.

#### 6-4 Inspection standar

|                          |                                                              |                                                                                    |               |                      |                 | 5 ( )          |  |  |  |  |

|--------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------|---------------|----------------------|-----------------|----------------|--|--|--|--|

| Item                     |                                                              | С                                                                                  | riterior      | n for defects        |                 | Defect<br>type |  |  |  |  |

| 1) Display on inspection | (1) Non display                                              |                                                                                    |               | (2) Vertical line is |                 | Major          |  |  |  |  |

|                          | (3) Horizontal line is deficient (4) Cross line is deficient |                                                                                    |               |                      |                 |                |  |  |  |  |

|                          | Size ⊕(mm) Acceptable number                                 |                                                                                    |               |                      |                 |                |  |  |  |  |

|                          | Φ≤0.3                                                        |                                                                                    | Ignore (note) |                      |                 |                |  |  |  |  |

| 2) Black / White spot    | 0.3<Ф≤                                                       |                                                                                    | ;             | 3                    |                 | Minor          |  |  |  |  |

|                          | 0.45<⊕                                                       | ≤0.6                                                                               | •             | 1                    |                 |                |  |  |  |  |

|                          | 0.3<⊕                                                        |                                                                                    |               | 0                    |                 |                |  |  |  |  |

|                          | (Note) Not                                                   | allowed if                                                                         | four m        | ore spots crowd      | together        |                |  |  |  |  |

|                          | Length (mm)                                                  | Width (m                                                                           | m)            | Acceptable nu        | mber            |                |  |  |  |  |

|                          | L≤10                                                         | W≤0                                                                                | .03           | Ignore               |                 |                |  |  |  |  |

|                          | 5.0≪L≪10                                                     | 0.03 <w≤< td=""><td>≤0.04</td><td>3</td><td></td><td></td></w≤<>                   | ≤0.04         | 3                    |                 |                |  |  |  |  |

| 3) Black / White line    | 5.0≤L≤10                                                     | 0.04 <w< td=""><td>≤0.05</td><td>2</td><td></td><td>Minor</td></w<>                | ≤0.05         | 2                    |                 | Minor          |  |  |  |  |

| o) Black / Write line    | 1.0≤L≤10                                                     | 0.05 <w≤< td=""><td>≨0.06</td><td>2</td><td></td><td>IVIII IOI</td></w≤<>          | ≨0.06         | 2                    |                 | IVIII IOI      |  |  |  |  |

|                          | 1.0≤L≤10                                                     | 0.06 <w≤< td=""><td>§0.08</td><td>1</td><td></td><td></td></w≤<>                   | §0.08         | 1                    |                 |                |  |  |  |  |

|                          | L≤10                                                         | W>80.0                                                                             |               | follows 2) po        | pint defect     |                |  |  |  |  |

|                          | Defects separate                                             | e with each                                                                        | n other       | at an interval of    | more than 20mm  |                |  |  |  |  |

| 4) Display pattern       |                                                              |                                                                                    |               |                      |                 |                |  |  |  |  |

|                          |                                                              |                                                                                    | [[            | Jnit: mm]            |                 |                |  |  |  |  |

|                          | <u>A+B</u> ≤0.45                                             | 0 <c td=""  d+i<=""><td><u>E</u>≤0.3</td><td>5 F+G≤0.35</td><td></td><td></td></c> | <u>E</u> ≤0.3 | 5 F+G≤0.35           |                 |                |  |  |  |  |

|                          | 2                                                            | 2                                                                                  |               | 1 <sub>2</sub>       |                 |                |  |  |  |  |

|                          | Note: 1) Up to 3                                             | damages                                                                            | accept        | able                 |                 |                |  |  |  |  |

|                          | 2) Not allo                                                  | wed if ther                                                                        | e are t       | wo or more pinh      | oles every 3 of |                |  |  |  |  |

|                          | fourths i                                                    |                                                                                    |               | ·                    | •               |                |  |  |  |  |

|                          |                                                              | Φ (mm)                                                                             | Ace           | ceptable Numbe       | r               |                |  |  |  |  |

|                          |                                                              | Φ ≤ 0.7                                                                            | +             | nore (note)          |                 |                |  |  |  |  |

| 5) 0 !!                  |                                                              | <Ф≤1.0                                                                             |               | 3                    |                 |                |  |  |  |  |

| 5) Spot-like contrast    |                                                              | <Φ≤1.5                                                                             |               | 1                    |                 | Minor          |  |  |  |  |

| irregularity             | 1.5                                                          | <Φ                                                                                 |               | 0                    |                 |                |  |  |  |  |

|                          | Note: 1) Conformed to limit samples.                         |                                                                                    |               |                      |                 |                |  |  |  |  |

|                          | 2)Intervals of defects are more than 30mm.                   |                                                                                    |               |                      |                 |                |  |  |  |  |

# LCD Module User Manual

| Item                                                     | Criterion for defects                                                                                                                                                                                                                        | Defect<br>type          |  |  |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|--|

| 6) Bubbles in polarizer                                  | $ \begin{array}{c cccc} Size & \Phi \text{ (mm)} & Acceptable Number \\ \hline & \Phi \leqslant 0.4 & Ignore \text{ (note)} \\ & 0.4 < \Phi \leqslant 0.65 & 2 \\ & 0.65 < \Phi \leqslant 1.2 & 1 \\ & 1.2 < \Phi & 0 \\ \end{array} $       | Minor                   |  |  |  |  |  |

| 7) Scratches and dent on the polarizer                   | Scratches and dent on the polarizer shall be in the accordance with "2) Black/white spot", and "3) Black/White line".                                                                                                                        | Minor                   |  |  |  |  |  |

| 8) Stains on the surface of LCD panel                    | Stains which cannot be removed even when wiped lightly with a soft cloth or similar cleaning.                                                                                                                                                | Minor                   |  |  |  |  |  |

| 9) Rainbow color                                         | No rainbow color is allowed in the optimum contrast on state within the active area.                                                                                                                                                         | Minor                   |  |  |  |  |  |

| 10) Viewing area encroachment                            | Polarizer edge or line is visible in the opening viewing area due to polarizer shortness or sealing line.                                                                                                                                    | Minor                   |  |  |  |  |  |

| 11) Bezel appearance                                     | Rust and deep damages that are visible in the bezel are rejected.                                                                                                                                                                            | Minor                   |  |  |  |  |  |

| 12) Defect of land surface contact                       | Evident crevices that are visible are rejected.                                                                                                                                                                                              | Minor                   |  |  |  |  |  |

| 13) Parts mounting                                       | <ol> <li>Failure to mount parts</li> <li>Parts not in the specifications are mounted</li> <li>For example: Polarity is reversed, HSC or TCP falls off.</li> </ol>                                                                            |                         |  |  |  |  |  |

| 14) Part alignment                                       | <ul><li>(1) LSI, IC lead width is more than 50% beyond pad outline.</li><li>(2) More than 50% of LSI, IC leads is off the pad outline.</li></ul>                                                                                             | Minor                   |  |  |  |  |  |

| 15) Conductive foreign matter (solder ball, solder hips) | <ul> <li>(1) 0.45&lt;Φ, N≥1</li> <li>(2) 0.3&lt;Φ≤0.45, N≥1         Φ: Average diameter of solder ball (unit: mm)</li> <li>(3) 0.5<l, li="" n≥1<=""> </l,></li></ul>                                                                         | Major<br>Minor<br>Minor |  |  |  |  |  |

| coldol Ilipo)                                            | L: Average length of solder chip (unit: mm)                                                                                                                                                                                                  | Willion                 |  |  |  |  |  |

| 16) PCB pattern damage                                   | (1) Deep damage is found on copper foil and the pattern is nearly broken.                                                                                                                                                                    | Major                   |  |  |  |  |  |

|                                                          | <ul><li>(2) Damage on copper foil other than 1) above</li><li>(1) Due to PCB copper foil pattern burnout, the pattern is</li></ul>                                                                                                           | Minor                   |  |  |  |  |  |

| 17) Faulty PCB correction                                | <ol> <li>Due to PCB copper foil pattern burnout, the pattern is connected, using a jumper wire for repair;2 or more places are corrected per PCB.</li> <li>Short-circuited part is cut, and no resist coating has been performed.</li> </ol> | Minor                   |  |  |  |  |  |

| 18) Bezel flaw                                           | Bezel claw missing or not bent                                                                                                                                                                                                               |                         |  |  |  |  |  |

| 19) Indication on name plate (sampling indication label) | <ol> <li>Failure to stamp or label error, or not legible.(all acceptable if legible)</li> <li>The separation is more than 1/3 for indication discoloration, in which the characters can be checked.</li> </ol>                               | Minor                   |  |  |  |  |  |

# 7.Reliability

#### 7-1 Lifetime

50,000 hours (25℃ in the room without ray of sun)

#### 7-2 Items of reliability

|     | Item                            | Condition                                                             | Criterion                                                                                                                          |

|-----|---------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|     | ligh<br>emperature<br>Operating | 60°C 96hrs                                                            | No cosmetic failure is allowable. Contrast ratio should be between initial value $\pm$                                             |

|     | Low<br>Temperature<br>Operation | -20℃ 96hrs                                                            | 10%. Total current consumption should be below double of initial value.                                                            |

| 3)  | Humidity                        | 40℃, 90%RH, 96hrs                                                     |                                                                                                                                    |

| 1 ' | High<br>Temperature             | <b>70</b> ℃ <b>96hrs</b>                                              | No cosmetic failure is allowable.  Contrast ratio should be between initial value +                                                |

| - / | Low<br>Temperature              | -30℃ 96hrs                                                            | 20%.  Total current consumption should be below                                                                                    |

| - / | Thermal shock                   | 25℃→30℃→25℃→70℃<br>5(min) 30(min) 5(min) 30(min)<br>5 cycle, 55~60%RH | double of initial value.                                                                                                           |

| 7)  | Vibration                       | 10~55~10hz<br>amplitude: 1.5mm<br>2hrs for each direction<br>(X,Y,Z)  | No defects in cosmetic and operational function are allowable.  Total current consumption should be below double of initial value. |

# 8. Handling Precautions

#### 8-1 Mounting method

A panel of LCD module consists of two thin glass plates with polarizers that easily get damaged.

And since the module in so constructed as to be fixed by utilizing fitting holes in the printed circuit board (PCB).

Extreme care should be used when handling the LCD modules.

#### 8-2 Cautions of LCD handling and cleaning

| When cleaning     | the display | surface, u | ise soft | cloth with | solvent | (recommended | below) |

|-------------------|-------------|------------|----------|------------|---------|--------------|--------|

| and wipe lightly. |             |            |          |            |         |              |        |

- ☐ Isopropyl alcohol☐ Ethyl alcohol

- Till of the

- □ Trichlorotriflorothane

Do not wipe the display surface with dry or hard materials that will damage the polarizer surface.

Do not use the following solvent:

- □ Water

- □ Ketone

- Aromatics

#### 8-3 Caution against static charge

The LCD module use C-MOS LSI drivers. So we recommend you:

Connect any unused input terminal to  $V_{dd}$  or  $V_{ss}$ . Do not input any signals before power is turned on, and ground your body, work/assembly areas, assembly equipment to protect against static electricity.

#### 8-4 Packaging

- Module employs LCD elements, and must be treated as such.

- Avoid intense shock and falls from a height.

- To prevent modules from degradation, do not operate or store them exposed direct to sunshine or high temperature/humidity.

## 8-5 Caution for operation

- It is an indispensable condition to drive LCD module within the limits of the specified voltage since the higher voltage over the limits may cause the shorter life of LCD module.

- An electrochemical reaction due to DC (direct current) causes LCD undesirable deterioration so that the uses of DC (direct current) drive should be avoided.

- Response time will be extremely delayed at lower temperature than the operating temperature range and on the other hand at higher temperature LCD module may show dark color in them. However those phenomena do not mean malfunction or out of order of LCD module, which will come back in the specified operating temperature.

#### 8-6 Storage

In the case of storing for a long period of time, the following ways are recommended:

- Storage in polyethylene bag with the opening sealed so as not to enter fresh air outside in it. And with not desiccant.

- Placing in a dark place where neither exposure to direct sunlight nor light is. Keeping the storage temperature range.

- Storing with no touch on polarizer surface by any thing else.

#### 8-7 Safety

- It is recommendable to crash damaged or unnecessary LCD into pieces and to wash off liquid crystal by either of solvents such as acetone and ethanol, which should be burned up later.

- When any liquid leaked out of a damaged glass cell comes in contact with your hands, please wash it off well at once with soap and water.

#### 9. Precautions for Use

- **9-1** Both parties should provide a limit sample on an occasion when both parties agree its necessity.

- The judgement by a limit sample shall take effect after the limit sample has been established and confirmed by both parties

- **9-2** On the following occasions, the handling of problem should be decided through discussion and agreement between responsible of the both parties.

- -When a question is arisen in this manual.

- -When a new problem is arisen which is not specified in this manual.

- -Some problem is arisen due to the change of inspection and operating conditions in users.

- -When a new problem is arisen at the customer's operating set for sample evaluation in the customer site.